Feng Mingliang's Blog, a programmer.

对嵌入式乐此不疲的程序员...

两篇关于ARM7启动代码分析的文章

Ps:读研的时候整天玩ARM7/9,仔细分析过周立功的一些启动代码,可以那时候没有写技术笔记的习惯,所以没留下来只字片言,今网上偶的一下两篇文章,觉得不错,特整理并转载。只是转载过程中发现一幅图没有,于是乎为了找到原文出处可是费了老劲了,不由得感慨,好多同志转载文章的时候太不负责了。这两篇文章整理如下。如需转载请注明出自 http://fml927.is-programmer.com。

文章1:基于ARM的硬件启动程序设计-初始化堆栈

文章2:周立功lpc21xx/lpc22xx系列ARM7启动代码分析

文章之一: 基于ARM的硬件启动程序设计-初始化堆栈

出自http://yxmyifeng.blog.163.com

ARM有7种运行状态,每一种状态的堆栈指针寄存器(SP)都是独立的。所以,对于程序中需要用的每一种处理器模式,都要给SP定义一个堆栈地址。流程为:修改状态寄存器内的状态位,使处理器切换到需要的模式,然后给SP赋值。需要注意的是:不要切换到User模式进行该模式下的堆栈设置,因为进入User模式后就不能再操作CPSR返回到其他模式了。

先定义各种模式对应的CPSR寄存器M[4:0]的值,该值决定了进入何种模式,可参考相关数据手册。

Mode_USR EQU 0x10 Mode_FIQ EQU 0x11 Mode_IRQ EQU 0x12 Mode_SVC EQU 0x13 Mode_ABT EQU 0x17 Mode_UND EQU 0x1B Mode_SYS EQU 0x1F I_BIT EQU 0x80 ; when I bit is set (1), IRQ is disabled F_BIT EQU 0x40 ; when F bit is set (1), FIQ is disabled

下面是初始化堆栈的代码段:

InitStack

MOV R0, LR; /* 设置管理模式堆栈 */

MSR CPSR_c, #(Mode_SVC | I_BIT | F_BIT) ; 0xd3

LDR SP, StackSvc

; /* 设置中断模式堆栈 */

MSR CPSR_c, #(Mode_IRQ | I_BIT | F_BIT) ; 0xd2

LDR SP, StackIrq

; /* 设置快速中断模式堆栈 */

MSR CPSR_c, #(Mode_FIQ | I_BIT | F_BIT) ; 0xd1

LDR SP, StackFiq

; /* 设置中止模式堆栈 */

MSR CPSR_c, #(Mode_ABT | I_BIT | F_BIT) ; 0xd7

LDR SP, StackAbt

; /* 设置未定义模式堆栈 */

MSR CPSR_c, #(Mode_UND | I_BIT | F_BIT) ; 0xdb

LDR SP, StackUnd

; /* 设置系统模式堆栈 */

MSR CPSR_c, #(Mode_SYS | I_BIT | F_BIT) ; 0xdf

LDR SP, StackUsr

MOV PC, R0

StackUsr DCD UsrStackSpace + (USR_STACK_LEGTH - 1) * 4

StackSvc DCD SvcStackSpace + (SVC_STACK_LEGTH - 1)* 4

StackIrq DCD IrqStackSpace + (IRQ_STACK_LEGTH - 1)* 4

StackFiq DCD FiqStackSpace + (FIQ_STACK_LEGTH - 1)* 4

StackAbt DCD AbtStackSpace + (ABT_STACK_LEGTH - 1)* 4

StackUnd DCD UndtStackSpace + (UND_STACK_LEGTH - 1)* 4

; /* 分配堆栈空间 */

AREA MyStacks, DATA, NOINIT, ALIGN=2

UsrStackSpace SPACE USR_STACK_LEGTH * 4 ;用户(系统)模式堆栈空间

SvcStackSpace SPACE SVC_STACK_LEGTH * 4 ;管理模式堆栈空间

IrqStackSpace SPACE IRQ_STACK_LEGTH * 4 ;中断模式堆栈空间

FiqStackSpace SPACE FIQ_STACK_LEGTH * 4 ;快速中断模式堆栈空间

AbtStackSpace SPACE ABT_STACK_LEGTH * 4 ;中止义模式堆栈空间

UndtStackSpace SPACE UND_STACK_LEGTH * 4 ;未定义模式堆栈

以管理模式堆栈空间为例说明一下。SVC_STACK_LEGTH 定义为 16 ,分配结果为:分配16个4字节的存储空间,把该存储空间初始化为0,并且把SP指向堆栈底部(内存高位)。

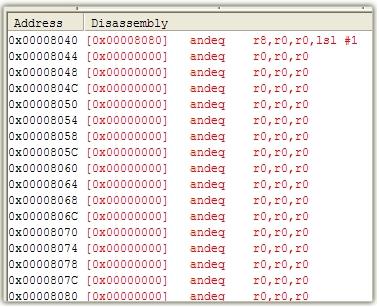

从上面memory的内容上面可以看出。管理模式堆栈分配了从0x00008080~0x00008044 一共16*4字节空间。其中0x00008040地址存储器上放置的是0x00008080,也就是该堆栈底部的指针的值。

就是说,StackSvc DCD SvcStackSpace + (SVC_STACK_LEGTH - 1)* 4 这条32位的伪指令,经过编译后,是在0x00008040(StackSvc)地址上放置SvcStackSpace地址值(0x00008080)。也就是把0x00008080赋给了SP了。

再看看地址0x00008080~0x00008044 上的内容,全部是andeq r0,r0,r0。从汇编指令格式来翻译,andeq r0,r0,r0翻译成16禁止代码后,刚好是0x00000000。

文章之二: 周立功lpc21xx/lpc22xx系列ARM7启动代码分析

整理得自http://ponymaggie.blog.sohu.com/116243391.html

网上已经有人做了一个周立功lpc2000(ARM7TDMI)启动代码分析的文章, 我本来想做一个s3c2410(ARM920T)的启动代码分析的, 但是看来了一下2410的启动代码,发现有些东西还不是理解的很清楚, 我ARM9的经验比较少.

所以还是做一个ARM7的启动代码分析吧, 网上那一份相比,我这个主要关注startup.s文件.网上那个startup.s几乎是一笔带过的。源码如下:

SVC_STACK_LEGTH EQU 0 FIQ_STACK_LEGTH EQU 0 IRQ_STACK_LEGTH EQU 256 ABT_STACK_LEGTH EQU 0 UND_STACK_LEGTH EQU 0 NoInt EQU 0x80 USR32Mode EQU 0x10 SVC32Mode EQU 0x13 SYS32Mode EQU 0x1f IRQ32Mode EQU 0x12 FIQ32Mode EQU 0x11

上面几行代码,不用过多分析, 定义几个符号而已, 把EQU想像成C中的#define就可以了. 具体定义的数值,下面的代码用到我再解释.

IMPORT __use_no_semihosting_swi

上面这一句的作用是在代码中禁用 semihosting 机制. 到底什么是semihostiong这里不多说, 网上有很多. 这里只说明Semihosting主要用来调试, 在release版本的代码中一般是要禁用的。

IMPORT FIQ_Exception IMPORT __main IMPORT TargetResetInit

上面三行是把要引入的外部标号声明一下,以便下面使用.

EXPORT bottom_of_heap EXPORT StackUsr EXPORT Reset EXPORT __user_initial_stackheap

上面四行是把要给其它文件使用的标号声明

AREA vectors,CODE,READONLY

ENTRY

上面这一行声明汇编文件的入口, 整个文件是从这里开始执行的.

Reset

LDR PC, ResetAddr

LDR PC, UndefinedAddr

LDR PC, SWI_Addr

LDR PC, PrefetchAddr

LDR PC, DataAbortAddr

DCD 0xb9205f80

LDR PC, [PC, #-0xff0]

LDR PC, FIQ_Addr

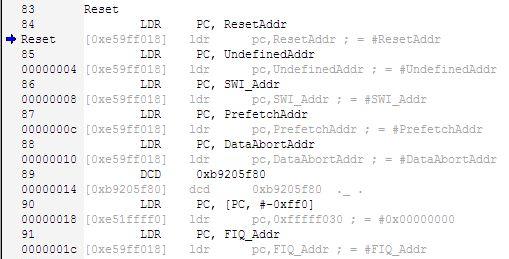

上面几行是配置中断向量表. 中断向量表的顺序是不能变的,因为这是ARM7规定的,可以参考相关书籍. 这里有几个问题要说明一下

.第一, 关于DCD 0xb9205f80, 按照ARM7的中断向量表分布图, 这个位置是个保留位. 但是究竟为什么要用0xb9205f80这个数值呢.

根据周立功的说法, nxp系列的lpc21xx,lpc22xx片子要求"中断向量表中所有数据32位累加和为0,否则程序不能脱机运行", 我在AXD反汇编了一下(如下图),把中断向量表中的8个机器码累加了一下:0xe59ff018*6+0xe51ffff0+0xb9205f80,没错, 结果是零. 但是我遇到一个问题, 就是我在实验中,把0xb9205f80这个数值改成任何值,程序运行都没问题. 头大了, 这个问题待解决中……(希望高手看到了可以指点一二)。

第二, 关于LDR PC, [PC, #-0xff0]. 这里本应该放IRQ中断的, 为什么是这么一句话. 其实在我blog的其中一篇文章里有提到过这一点。

ARM7的三级流水线结构导致了PC指向的是当前指令的后8个字节. 本来IRQ是应该放在0x00000018处的. LDR PC, [PC, #-0xff0]这条语句执行后, PC的当前值就是0x00000018+8-0xff0. 很容易计算出它的结果是0xfffff030. 看一下lpc22xx的手册就知道. 这个地址就是VICVectAddr. 也就是说本来这个地址是应该放IRQ服务程序的入口地址的,但是这个地址被放在了VICVectAddr 这个寄存器里. 英文手册里有一段对VICVectAddr 描述. 看了之后就容易明白是怎么回事了: Vector Address Register. When an IRQ interrupt occurs, the IRQ service routine can read this register and jump to the value read

ResetAddr DCD ResetInit UndefinedAddr DCD Undefined SWI_Addr DCD SoftwareInterrupt PrefetchAddr DCD PrefetchAbort DataAbortAddr DCD DataAbort Nouse DCD 0 IRQ_Addr DCD 0 FIQ_Addr DCD FIQ_Handler

这几行是为上面中断向量表中的中断标号分配内存空间, 也就是它们的执行地址. 一开始我有个疑问, 为什么不直接用LDR PC, ResetInit,还要用DCD中转一下, 后来上网查了一下,才恍然大悟, ldr指令中的地址必须为当前指令地址是4KB范围内, 用DCD中转一下就可以在整个程序空间寻址。

Undefined

B Undefined

SoftwareInterrupt

B SoftwareInterrupt

PrefetchAbort

B PrefetchAbort

DataAbort

B DataAbort

FIQ_Handler

STMFD SP!, {R0-R3, LR}

BL FIQ_Exception

LDMFD SP!, {R0-R3, LR}

SUBS PC, LR, #4

这几行不用过多解释, 只是说明上面几个异常如何执行。

评论 (0)

评论 (0)